# **DC-SCM LTPI IP Core - Lattice Propel Builder**

## **User Guide**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults and associated risk the responsibility entirely of the Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## **Contents**

| Acronym          | ns in This Document                   | 6  |

|------------------|---------------------------------------|----|

| 1. Intr          | oduction                              | 7  |

| 1.1.             | Quick Facts                           | 7  |

| 1.2.             | Features                              | 7  |

| 1.3.             | Conventions                           | 8  |

| 1.3.             | .1. Nomenclature                      | 8  |

| 1.3.             | .2. Signal Names                      | 8  |

| 1.3.             | .3. Attribute Names                   | 8  |

| 2. Fun           | nctional Descriptions                 | 9  |

| 2.1.             | Overview                              | 9  |

| 2.2.             | Signal Description                    | 10 |

| 2.3.             | Attribute Summary                     | 13 |

| 2.4.             | Register Description                  | 19 |

| 2.5.             | Implementation Flow                   | 25 |

| 2.5.             | .1. Tunneling                         | 25 |

| 2.5.             | .2. State Machine                     | 26 |

| 2.6.             | Frame Format                          | 29 |

| 2.6.             | .1. Frame Format                      | 29 |

| 2.6.             | .2. Different Frame Formats           | 29 |

| 2.6.             | .3. CRC                               | 37 |

| 2.6.             | .4. Frame Interleave                  | 37 |

| 2.7.             | Functional Blocks                     |    |

| 2.7.             | .1. Multiplexor                       | 37 |

| 2.7.             | •                                     |    |

| 2.7.             |                                       |    |

| 2.7.             |                                       |    |

| 2.7.             | ·                                     |    |

| 2.7.             |                                       |    |

| 2.8.             | IP Programming Sequence               |    |

| 2.8.             |                                       |    |

| 2.8.             | •                                     |    |

| 2.9.             | ·                                     |    |

| 2.9.             | _                                     |    |

| 2.9.             |                                       |    |

| 2.9.             |                                       |    |

| 2.9.             |                                       |    |

| 2.9.             |                                       |    |

| 2.10.            | Clocks and Reset                      |    |

| _                | 0.1. Clock Computations               |    |

|                  | 0.2. Sample Clock Computations        |    |

|                  | 0.3. Clock Compensation               |    |

|                  | 0.4. Reset                            |    |

|                  | Error Impact, Handling, and Recovery  |    |

| 2.11.<br>Annondi | · · · · · · · · · · · · · · · · · · · |    |

|                  | ix A. Resource Utilization            |    |

| • •              | ix B. Limitations                     |    |

|                  | Ces                                   |    |

|                  | al Support Assistance                 |    |

| kevision         | History                               | 62 |

## **Figures**

| Figure 2.1. High-Level Block Diagram                                              | 9  |

|-----------------------------------------------------------------------------------|----|

| Figure 2.2. Functional Block Diagram of DC-SCM LTPI set as either SCM or HPM      | 9  |

| Figure 2.3. DC-SCM LTPI End-to-End SCM to HPM Connection Functional Block Diagram | 10 |

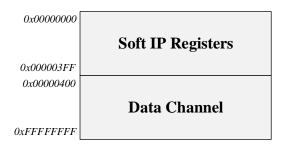

| Figure 2.4. Register Address Space                                                | 19 |

| Figure 2.5. Tunneling Diagram                                                     | 25 |

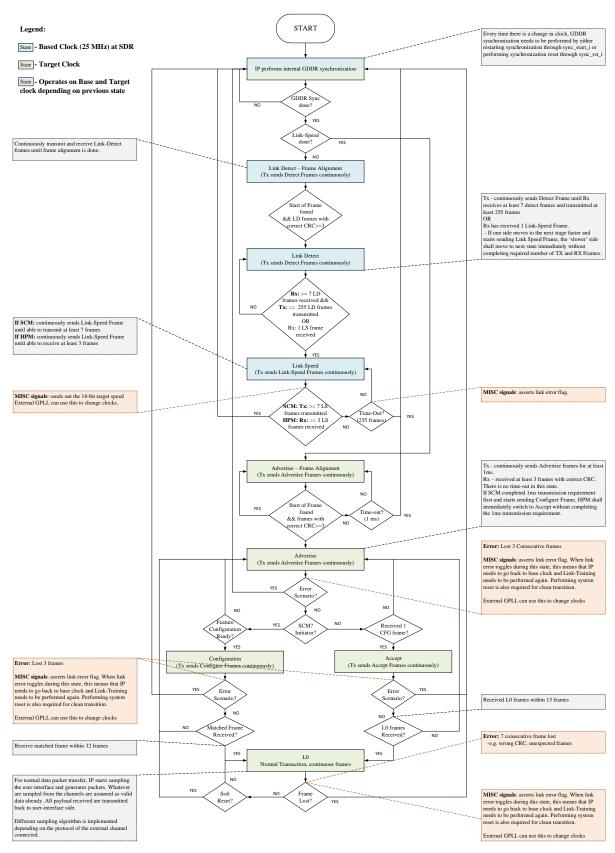

| Figure 2.6. FSM of DC-SCM LTPI IP                                                 | 26 |

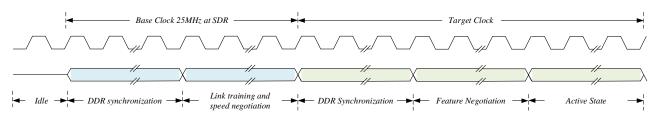

| Figure 2.7. PHY States                                                            | 27 |

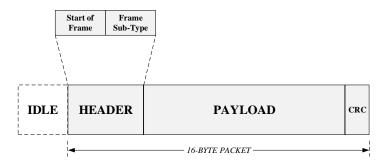

| Figure 2.8 Frame Illustration                                                     | 29 |

| Figure 2.9. LTPI_VER Byte Mapping                                                 | 30 |

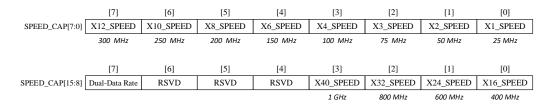

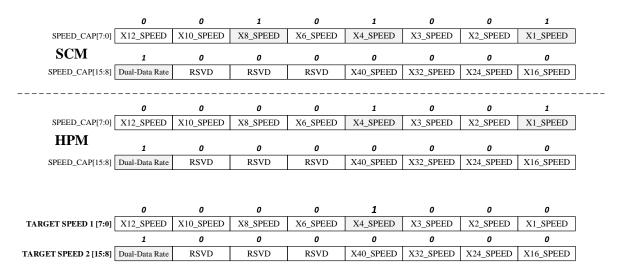

| Figure 2.10. SPEED_CAP Byte Mapping                                               |    |

| Figure 2.11. Target Speed Processing Illustration                                 |    |

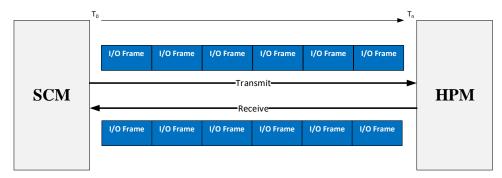

| Figure 2.12. LTPI Frame Stream without Data Channel                               |    |

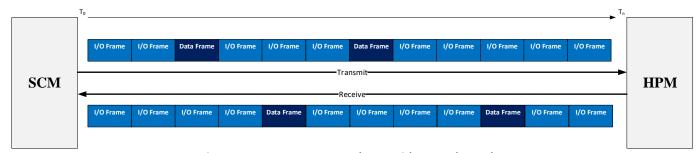

| Figure 2.13. LTPI Frame Interleave with Data Channel                              |    |

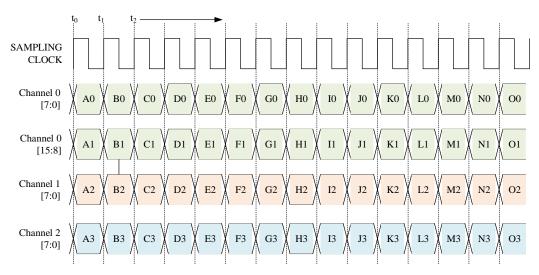

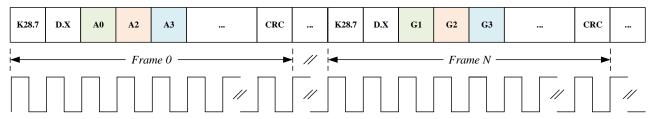

| Figure 2.14. Sample waveform                                                      |    |

| Figure 2.15. Resulting Frame                                                      | 38 |

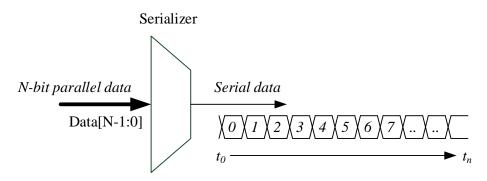

| Figure 2.16. Parallel to Serial Conversion Order                                  | 39 |

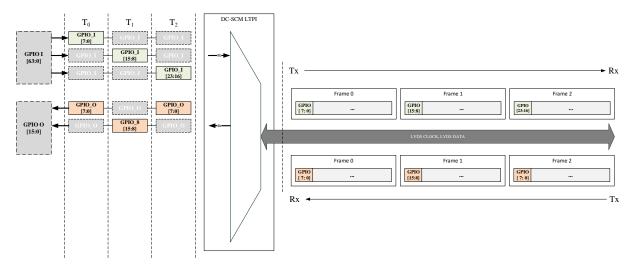

| Figure 2.17. GPIO Pin List                                                        |    |

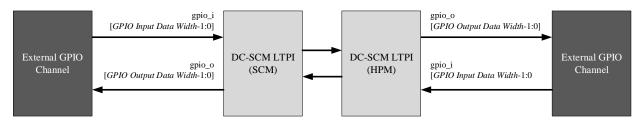

| Figure 2.18. GPIO Mechanism                                                       | 42 |

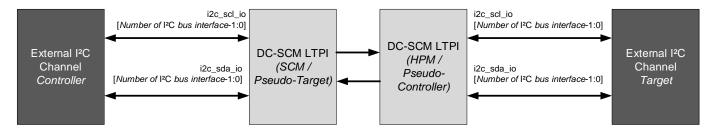

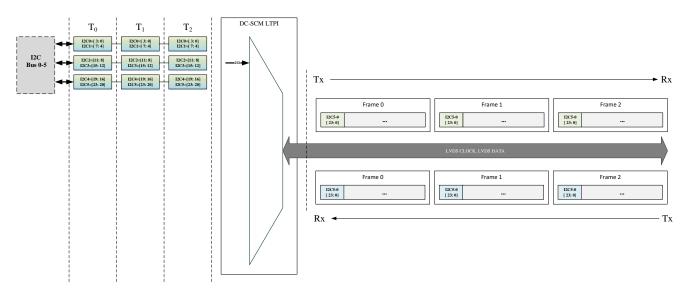

| Figure 2.19. I <sup>2</sup> C Pin List                                            | 42 |

| Figure 2.20. I <sup>2</sup> C Mechanism                                           |    |

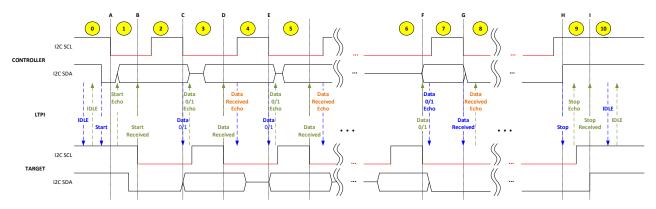

| Figure 2.21. I <sup>2</sup> C Bus Event Exchange Between Controller and Target    | 43 |

| Figure 2.22. UART Pin List                                                        | 47 |

| Figure 2.23. UART General Oversampling Principle                                  | 47 |

| Figure 2.24. LTPI UART Sampling Distribution                                      |    |

| Figure 2.25. UART Mechanism                                                       | 48 |

| Figure 2.26. OEM Pin List                                                         |    |

| Figure 2.27. OEM Mechanism                                                        | 49 |

| Figure 2.28. Data Channel Pin List                                                |    |

| Figure 2.29. APB Interface for SCM and HPM                                        |    |

| Figure 2.30. Example of Data Channel Usage                                        |    |

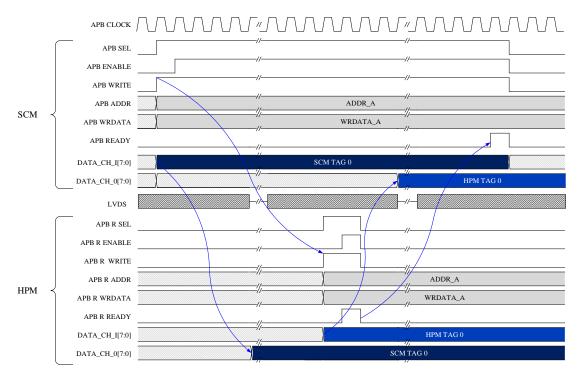

| Figure 2.31. Sample SCM to HPM APB Transaction                                    |    |

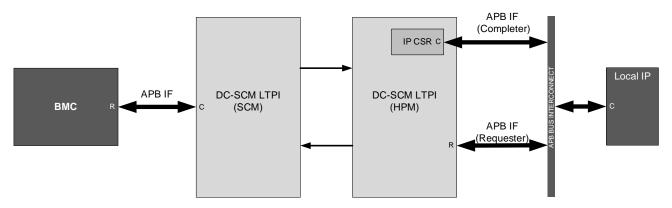

| Figure 2.32. Sample HPM IP CSR Access Through Data Channel Block Diagram          |    |

| Figure 2.33. General Clocking Topology (Main)                                     |    |

| Figure 2.34. Suggested Clocking Implementation (Follower)                         | 54 |

| Figure 2.35. End to End Clocking Implementation                                   | 55 |

## **Tables**

| Table 1.1. DC-SCM LTPI IP Quick Facts                                         | 7  |

|-------------------------------------------------------------------------------|----|

| Table 2.1. DC-SCM LTPI IP Core Signal Description                             | 10 |

| Table 2.2. Attributes Table                                                   | 13 |

| Table 2.3. Attributes Description                                             | 16 |

| Table 2.4. DC-SCM LTPI Soft IP Registers                                      | 19 |

| Table 2.5. Access Type Definition                                             | 25 |

| Table 2.6. Frame Format Contents                                              | 29 |

| Table 2.7 Link-Detect Frame Format                                            | 29 |

| Table 2.8. Link-Speed Frame Format                                            | 30 |

| Table 2.9. Advertise Frame Format                                             | 31 |

| Table 2.10. Platform Field Bit Mapping                                        | 31 |

| Table 2.11. Capabilities Type Details                                         |    |

| Table 2.12. Feature Capability Mapping for Default I/O Frame (0x00)           | 32 |

| Table 2.13. Feature Capability Mapping for Custom I/O Frame (0x81)            | 32 |

| Table 2.14. Feature Capability Mapping for OEM Defined (0x82-0xFF)            | 33 |

| Table 2.15. UART Baud Rate Encoding                                           | 33 |

| Table 2.16. Configure Frame Format                                            | 33 |

| Table 2.17. Accept Frame Format                                               | 34 |

| Table 2.18. Data Frame Type Summary                                           | 35 |

| Table 2.19. Sample Custom I/O Format                                          | 35 |

| Table 2.20. Default I/O Format                                                | 36 |

| Table 2.21. Data Frame General Format                                         |    |

| Table 2.22. Tunneling Principles for Different Channels                       | 40 |

| Table 2.23. Sample Customized Payload Configuration                           |    |

| Table 2.24. I <sup>2</sup> C Events Encoding                                  |    |

| Table 2.25. I <sup>2</sup> C Event Payload Mapping                            |    |

| Table 2.26. I <sup>2</sup> C Event Request Flow                               |    |

| Table 2.27. UART Bus Content                                                  |    |

| Table 2.28. Data Channel Command Encoding                                     | 50 |

| Table 2.29. Memory Command Frame Mapping                                      |    |

| Table 2.30. Data Mapping for Operation Status and Byte Enable of Data Channel |    |

| Table 2.31. Summary of Data Channel CRC handling                              | 53 |

| Table 2.32. IP Error Handling                                                 | 56 |

| Table 2.33. CRC Error Impact on LTPI Channels                                 | 56 |

| Table 2.34. Timeout Impact on LTPI Channels                                   | 57 |

| Table A.1. Resource Utilization                                               | 58 |

6

## **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym  | Definition                                                                                                                            |

|----------|---------------------------------------------------------------------------------------------------------------------------------------|

| AMBA     | Advanced Microcontroller Bus Architecture                                                                                             |

| APB      | Advanced Peripheral Bus                                                                                                               |

| ATM      | Asynchronous Transfer Mode                                                                                                            |

| ВМС      | Baseboard Management Controller                                                                                                       |

| CCITT    | International Telegraph and Telephone Consultative Committee (French: Comité Consultatif International Téléphonique et Télégraphique) |

| CRC      | Cyclic Redundancy Check                                                                                                               |

| DC-SCI   | Datacenter-ready Secure Control Interface                                                                                             |

| DC-SCM   | Datacenter-ready Secure Control Module                                                                                                |

| GUID     | Globally Unique Identifier                                                                                                            |

| HEC      | Header Error Control                                                                                                                  |

| НРМ      | Host Processor Module                                                                                                                 |

| HPM FPGA | Host Processor Module FPGA                                                                                                            |

| LVDS     | Low Voltage Differential Signaling                                                                                                    |

| LTPI     | LVDS Tunneling Protocol and Interface                                                                                                 |

| MCSI     | Multi-Channel Serial Interface                                                                                                        |

| TDM      | Time Division Multiplexing                                                                                                            |

## 1. Introduction

The Lattice Semiconductor DC-SCM LVDS Tunneling Protocol and Interface (LTPI) IP Core is an Open Computer Project (OCP) Data Center – Secure Control Module (DC-SCM) Standards compatible solution which is introduced in the DC-SCM 2.0 Specification. DC-SCM aims to move common server management, security and control features from a typical motherboard into a module designed in different form factors (horizontal, vertical). The basic idea is to enable a common security and management module form and interface which can be used across datacenter platforms.

From a Data Center perspective, DC-SCM enables a common management and security to be deployed across a higher percentage of platforms. It also enables deployment of management and security upgrades on platforms within a generation without redesign of more complex components. From development perspective, this enables solution providers to remove customer specific solutions from the more complex components (such as motherboards). This enables greater leverage of higher complexity components across platforms.

LTPI is a protocol and interface designed for tunneling various low-speed signals between HPM and SCM. The LTPI protocol goes over the LVDS (Low Voltage Differential Signals) electrical interfaces supported by majority of the CPLDs and FPGAs. This is the next generation protocol for DC-SCM 2.0 as the replacement to two Serial GPIO (SGPIO) interfaces. The LVDS interface provides higher bandwidth and better scalability than the SGPIO interface. It allows for tunneling of not only GPIOs but also low speed serial interfaces such as I<sup>2</sup>C and UART. It is also extensible with additional proprietary OEM interfaces and provides support for raw Data tunneling between HPM CPLD and SCM CPLD.

Also, the DC-SCM LTPI IP Core provides a solution for minimal wire connection between two FPGAs to provide TDM-based bidirectional communication, aggregating multiple data such as I<sup>2</sup>C, GPIO and UART to add more flexibility to a customer's system and board design. This solution is compliant with Datacenter-ready Secure Control Module (DC-SCM) 2.0.

## 1.1. Quick Facts

Table 1.1 presents a summary of the DC-SCM LTPI IP.

Table 1.1. DC-SCM LTPI IP Quick Facts

| IP Requirements            | Supported FPGA Families  | MachXO3L™, MachXO3LF™, MachXO3D™                                                                       |  |  |

|----------------------------|--------------------------|--------------------------------------------------------------------------------------------------------|--|--|

|                            | Targeted Devices         | LCMXO3L, LCMXO3LF, LCMXO3D                                                                             |  |  |

| Resource Utilization       | Supported User Interface | GPIO, I <sup>2</sup> C, UART, OEM, Data to LVDS and vice versa                                         |  |  |

|                            | Resources                | See Table A.1.                                                                                         |  |  |

|                            | Lattice Implementation   | IP Core v1.1.x – Lattice Propel™ Builder 2.1                                                           |  |  |

|                            | Sunthasis                | Lattice Synthesis Engine                                                                               |  |  |

| <b>Design Tool Support</b> | Synthesis                | Synopsys® Synplify Pro® for Lattice                                                                    |  |  |

|                            | Simulation               | For a list of supported simulators, see the Lattice Radiant™ and Lattice Diamond® software user guide. |  |  |

#### 1.2. Features

The key features of the DC-SCM LTPI IP include:

- Compliant with OCP DC-SCM 2.0 LTPI 1.0 Specifications

- Link initialization, discovery and negotiation.

- Supports Multi-Channel Serial Interface

- Supports LVDS

- Supports up to 5 channels aggregation/disaggregation in total

- Supports GPIO, I<sup>2</sup>C, UART, OEM, and Data channel aggregation

- For I<sup>2</sup>C interface, each can be configured as Controller, Target or Controller/Target (for multi-controller/main).

- Supports up to 800 Mbps LVDS data rate for MachXO3™ family devices

- Supports AMBA 3 APB Protocol v1.0 for register access of the soft IP and Data Channel

- Supports PREADY, a ready signal to indicate completion of an APB transfer

- PSLVERR is only supported in Data Channel related access (error signal indicating failure of a transfer)

### 1.3. Conventions

#### 1.3.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

### 1.3.2. Signal Names

Signal names that end with:

- \_n are active low (asserted when value is logic 0)

- \_*i* are input signals

- \_o are output signals

- \_io are bidirectional signals

#### 1.3.3. Attribute Names

Attribute names in this document are formatted in title case and italicized (Attribute Name).

9

## 2. Functional Descriptions

### 2.1. Overview

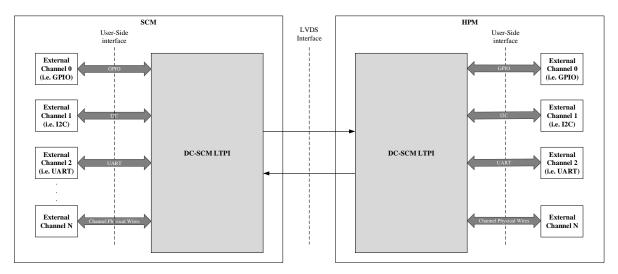

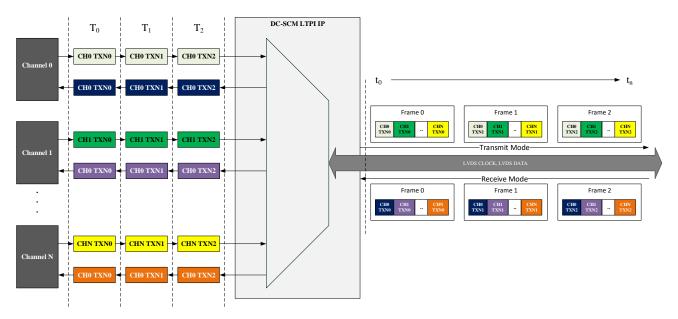

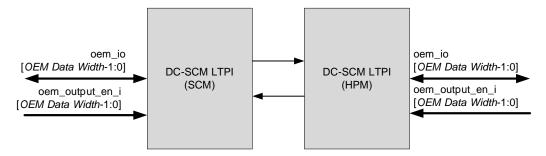

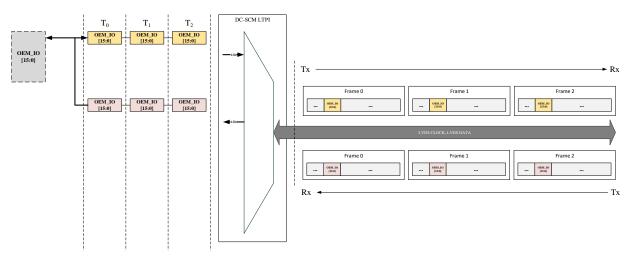

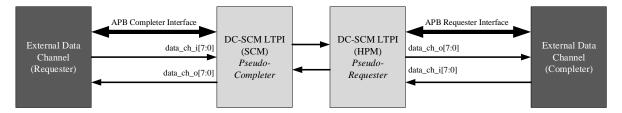

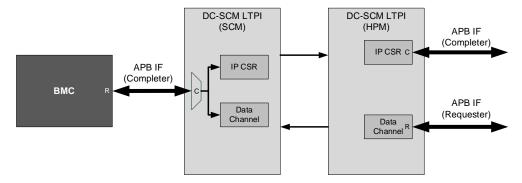

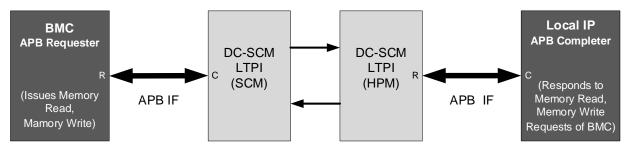

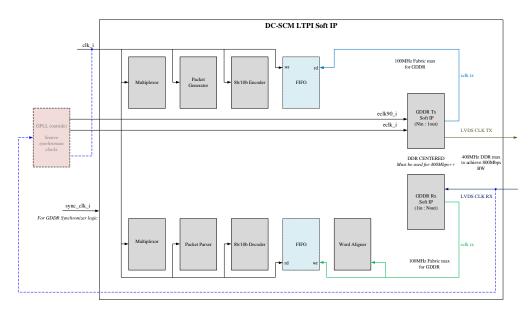

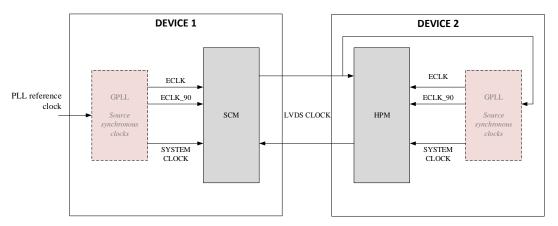

High-level block diagram of DC-SCM LTPI IP is shown in Figure 2.1. Data received from external channels are aggregated and transmitted from SCM side to Host Processor Module (HPM) through Low Voltage Differential Signaling (LVDS). Data received from HPM is de-aggregated and remapped to external channels.

Figure 2.1. High-Level Block Diagram

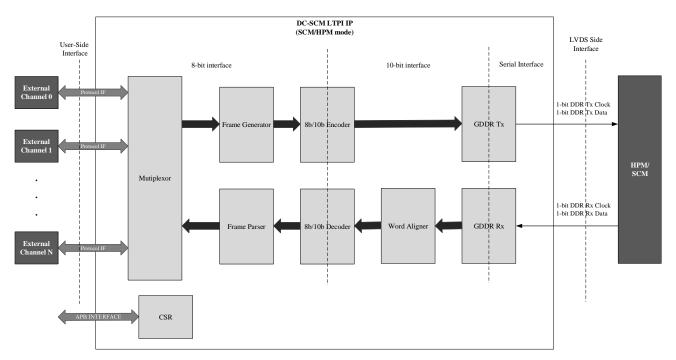

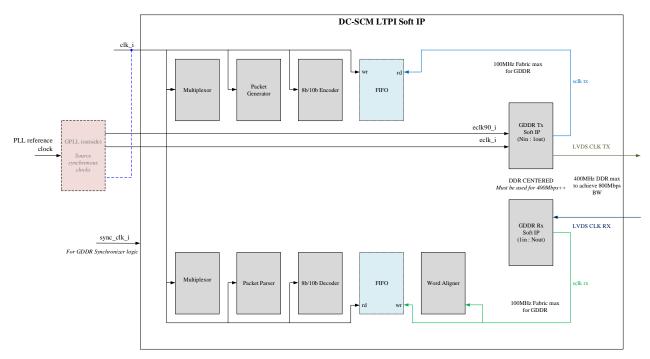

The functional block diagram of DC-SCM LTPI IP set as either "SCM" or "HPM" is shown in Figure 2.2.

Figure 2.2. Functional Block Diagram of DC-SCM LTPI set as either SCM or HPM

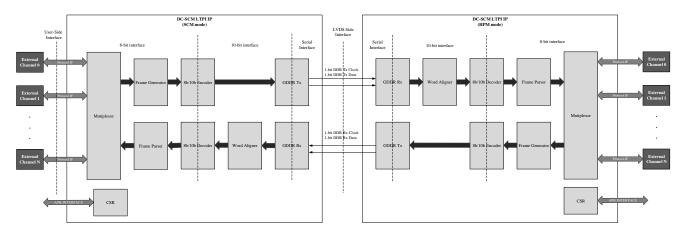

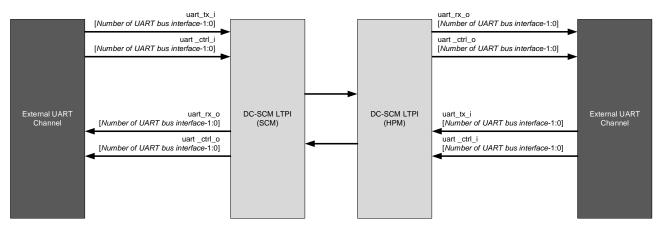

Figure 2.3 shows a complete end-to-end block diagram of the SCM to HPM modules.

Figure 2.3. DC-SCM LTPI End-to-End SCM to HPM Connection Functional Block Diagram

DC-SCM/HPM LTPI IP is consists of Multiplexor, Frame Generator/Parser, 8b/10b Encoder/Decoder, Word Aligner/Link Synchronizer and GDDR Transmit and Receive modules. In transmit mode, direction of data flow is from Multiplexor to GDDR Tx. In receive mode, the data path is from GDDR Rx to Multiplexor. An instance of this IP has both Rx and Tx paths available that work simultaneously.

Data received from the user-side are considered valid data streams for transmit. Payload within frames received are considered valid.

## 2.2. Signal Description

Table 2.1. DC-SCM LTPI IP Core Signal Description

| Port Name    | I/O    | Width | Default Value | Description                                                                                                                                                                                                                    |

|--------------|--------|-------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System       | 1 ., 0 |       | Delaule Value | 2 Cost Iption                                                                                                                                                                                                                  |

| eclk_i       | I      | 1     | N/A           | GDDR fast sampling clock. Same frequency as LVDS Clock (MHz)                                                                                                                                                                   |

| eclk90_i     | I      | 1     | N/A           | 90-degree shifted for transmit clock generation.  Same frequency as LVDS Clock (MHz) and must be source synchronous with eclk_i.                                                                                               |

| sync_clk_i   | I      | 1     | N/A           | GDDR_SYNC low speed continuously running clock input.  Must be slower or equal than the slowest clock in the system.                                                                                                           |

| sync_rst_i   | I      | 1     | N/A           | Active-high GDDR synchronization reset.                                                                                                                                                                                        |

| sync_start_i | ı      | 1     | N/A           | Start the GDDR sync process of both PHY Tx and Rx. Must be asserted only if all clocks (Rx and Tx) are already stable. Must be HIGH during all synchronization process.  Can be tied to GPLL lock of source synchronous clocks |

| clk_i        | I      | 1     | N/A           | Input system clock used to clock both Tx and Rx logic.  Frequency should be equivalent to LVDS Clock (MHz) / PHY_MODE  PHY_MODE = 5 (for DDR)  PHY_MODE = 10 (for SDR)                                                         |

| reset_n_i    | į      | 1     | N/A           | Active-low system reset                                                                                                                                                                                                        |

| sys_clk_o    | 0      | 1     | N/A           | Output Rx SCLK generated by the IP. This is based on DDR system used.  Frequency is equivalent to LVDS Clock (MHz)/ (DDR_GEAR/DDR_MODE)  DDR_GEAR = 8 (MachXO3);  DDR_MODE = 2 (for DDR); DDR_MODE = 1 (for SDR)               |

| soft_reset_i | I      | 1     | N/A           | Soft-reset of the system                                                                                                                                                                                                       |

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Port Name                                       | I/O             | Width                          | Default Value           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------|-----------------|--------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                 |                 |                                |                         | Reset only applies to interface controller and Link-training and negotiation FSM-related logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| start_tx_i                                      | I               | 1                              | N/A                     | External control to start Tx path process. When asserted, IP starts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                 |                 |                                |                         | link-training and negotiations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                 |                 |                                |                         | Must be HIGH during all IP process. If deasserted, system reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                 | _               | _                              |                         | must also be performed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| start_rx_i                                      |                 | 1                              | N/A                     | External control to start Rx path process. When asserted, IP starts link-training and negotiations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                 |                 |                                |                         | Must be HIGH during all IP process. If deasserted, system reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                 |                 |                                |                         | must also be performed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| int_o                                           | 0               | 1                              | 1'b0                    | Interrupt signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Protocol Information <sup>8</sup>               |                 |                                | •                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| tgt_spd_o                                       | 0               | 16                             | 16'h0                   | Indicates the target speed of the link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| tgt_spd_vld_o                                   | 0               | 1                              | 1'b0                    | Indicates valid target speed of the link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| rx_feat_cap_o                                   | 0               | 64                             | 64'h0                   | Received feature capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| rx_feat_cap_vld_o                               | 0               | 1                              | 1'b0                    | Received feature capability valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                 | 0               | 1                              | 1'b0                    | Indicates clock can be reconfigured for target frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| clkcfg_en_o                                     |                 |                                |                         | This is asserted the first time IP goes to Advertise state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LVDS Interface                                  |                 |                                |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| lvds_tx_clk_o                                   | 0               | 1                              | N/A                     | Differential Tx PHY clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| lvds_tx_data_o                                  | 0               | 1                              | N/A                     | Differential Tx PHY data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| lvds_rx_clk_i                                   | Ι               | 1                              | N/A                     | Differential Rx PHY clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| lvds_rx_data_i                                  | I               | 1                              | N/A                     | Differential Rx PHY data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Low Latency GPIO Cha                            | nnel Int        | erface <sup>1</sup>            |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Il_gpio_i                                       | I               | LL GPIO                        | N/A                     | GPIO input pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |